MMDC 接口与 STM32 的 FSMC 接口雷同好看的欧美情色电影,只不外 MMDC 接口专用于外接 DDR,而且 MMDC 外部引脚不复用。MMDC 是一个多模的 DDR 为止器,不错趋承 16 位宽的 DDR3/DDR3L、16 位宽的 LPDDR2。

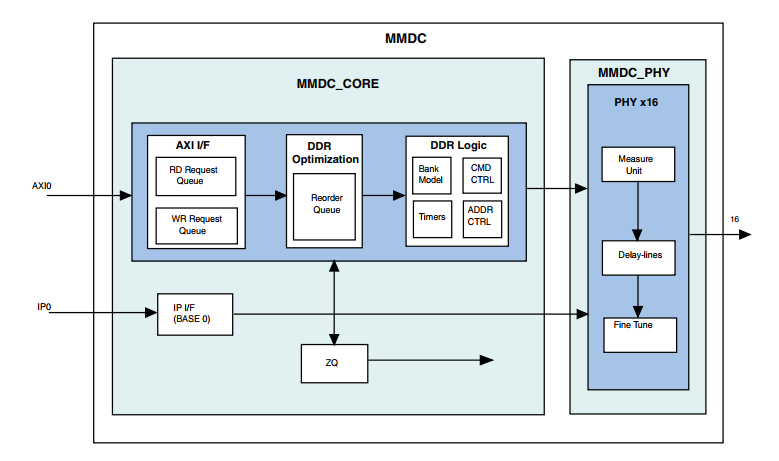

MMDC 是一个可建设、高性能的 DDR 为止器。MMDC 外设包含一个内核(MMDC_CORE)和 PHY(MMDC_PHY),内核和 PHY 的功能如下:

MMDC_CORE肃肃通过 AXI 接口与系统进行通讯,达成 DDR 大喊生成、DDR 大喊优化和读写数据旅途。为止所有 MMDC 的功能达成。

MMDC_PHY肃肃时序调整和校准,使用荒芜的校准机制以确保数据被平常收发, 最高救助 400MHz。

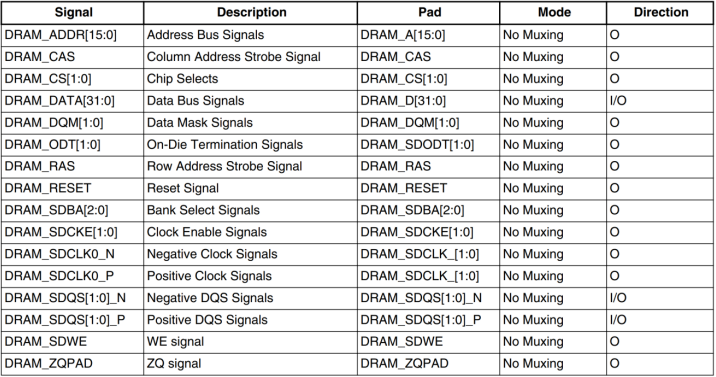

1.1 MMDC信号引脚在使用 STM32 的时候 FMC/FSMC 的 IO 引脚是带有复辛勤能的,若是不接 SRAM 或 SDRAM 的话 FMC/FSMC 是不错用作其他外设 IO 的。然则,关于 DDR 接口就不一样了,因为 DDR 关于硬件条款相等严格,因此 DDR 的引脚都是孤独的,一般莫得复辛勤能,只作念为 DDR 引脚使用。I.MX6U 也有专用的 DDR 引脚如下:

1.2 MMDC时钟源

1.2 MMDC时钟源

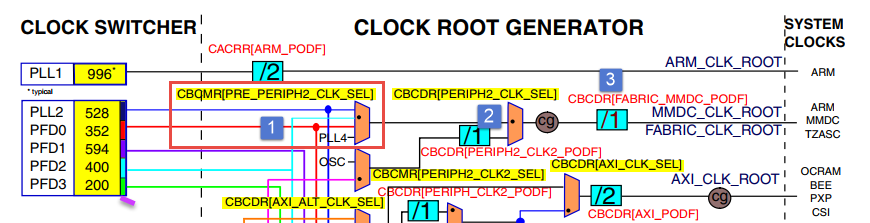

默许情况下 PLL2 的 PFD2 时钟输出看成 MMDC 的根时钟,时钟频率为 400MHz(试验396MHz)。时钟产生旅途如下图所示:

PLL2 的 PFD2 历程两个时钟聘任寄存器(标号①和②)和一个时钟分频寄存器(标号③)之后趋承到 MMDC_CLK_ROOT。具体寄存器在时钟树中也曾标出。终点注宗旨是,在时势中不成放纵修改时钟聘任寄存器以实时钟分频寄存器,因为时势平常运行会使用 DDR,而不正确的修改 DDR 根时钟会形成系统崩溃。二、DDR简介

DDR 内存是 SDRAM 的升级版块,SDRAM 分为 SDR SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM。

DDR 全称是 Double Data Rate SDRAM,也便是双倍速率 SDRAM,看名字就知谈 DDR 的速率(数据传输速率)比 SDRAM 高 1 倍!这 1 倍的速率不是纯粹略单的将 CLK 培育 1 倍,SDRAM 在一个 CLK 周期传输一次数据,DDR 在一个 CLK 周期传输两次数据,也便是在飞腾沿和着落沿各传输一次数据,这个见地叫作念预取(prefetch),十分于 DDR 的预取为 2bit,因此 DDR 的速率径直加倍!比如 SDRAM 速率一般是 133~200MHz,对应的传输速率便是 133~200MT/s,在刻画 DDR 速率的时候一般都使用 MT/s,也便是每秒些许兆次数据传输。133MT/S 便是每秒 133M 次数据传输,MT/s 刻画的是单元技术内传输速率。相通 133~200MHz 的频率,DDR 的传输速率就变为了 266~400MT/S,是以全球常说的 DDR266、DDR400 便是这样来的。

DDR2 在 DDR 基础上进一步加多预取(prefetch),加多到了 4bit,十分于比 DDR 多读取一倍的数据,因此 DDR2 的数据传输速率便是 533~800MT/s,这个也便是全球常说的 DDR2 533、DDR2 800。固然了,DDR2 还有其他速率,这里仅仅说最常见的几种。

DDR3 在 DDR2 的基础上将预取(prefetch)培育到 8bit,因此又得回了比 DDR2 高一倍的传输速率,因此在总线时钟相通为 266~400MHz 的情况下,DDR3 的传输速率便是 1066~1600MT/S。I.MX6U 的 MMDC 外设用于趋承 DDR,救助 LPDDR2、DDR3、DDR3L,最高救助 16 位数据位宽。总线速率为 400MHz(试验是 396MHz),数据传输速率最大为 800MT/S。这里咱们讲一下 LPDDR3、DDR3 和 DDR3L 的区别,这三个都是 DDR3,然则区别主要在于责任电压,LPDDR3 叫作念低功耗 DDR3,责任电压为 1.2V。DDR3 叫作念标压 DDR3,责任电压为 1.5V,一般台式内存条都是 DDR3。DDR3L 是低压 DDR3,责任电压为 1.35V,一般手机、镶嵌式、札记本等都使用 DDR3L。

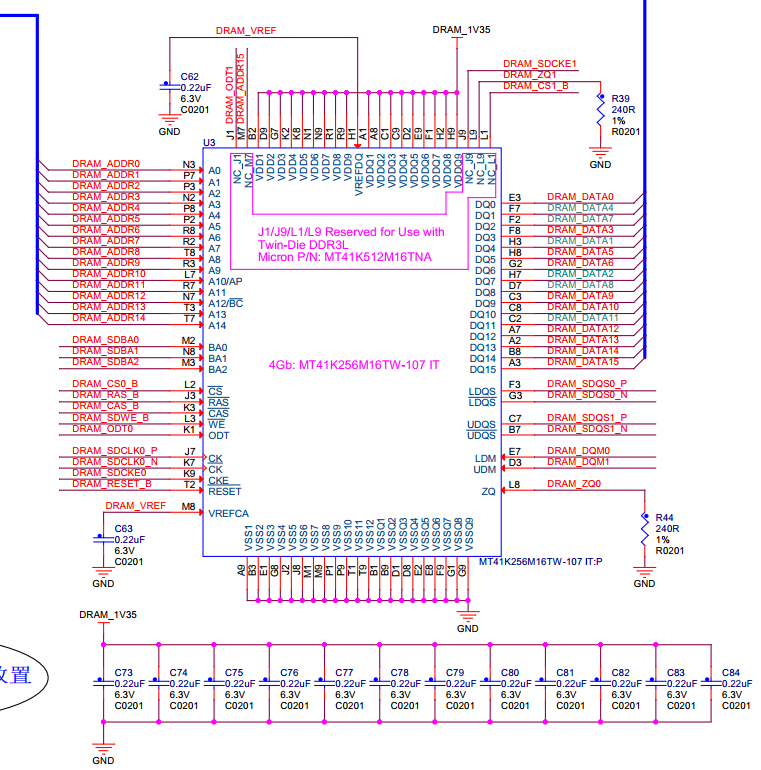

三、引脚细目我使用的是 野火_EBF6ULL S1 Pro 设备板,DDR型号是 MT41K256M16TW-107,容量 256M*16 共 512M 字节,数据宽度 16 位。

色戒完整未删版在线看

四、DDR3测试4.1 下载DDR测试软件和建设文献

NXP 提供了一个相等好用的 DDR 测试软件,叫作念 ddr_stress_tester。官网下载:https://community.nxp.com/docs/DOC-102005百度网盘:

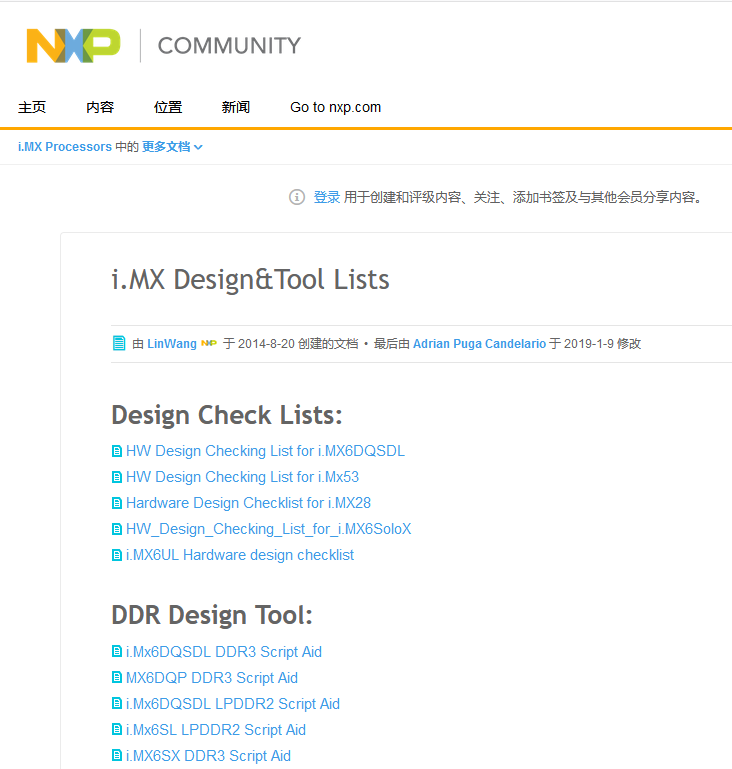

翻开下载地址,如下图所示。

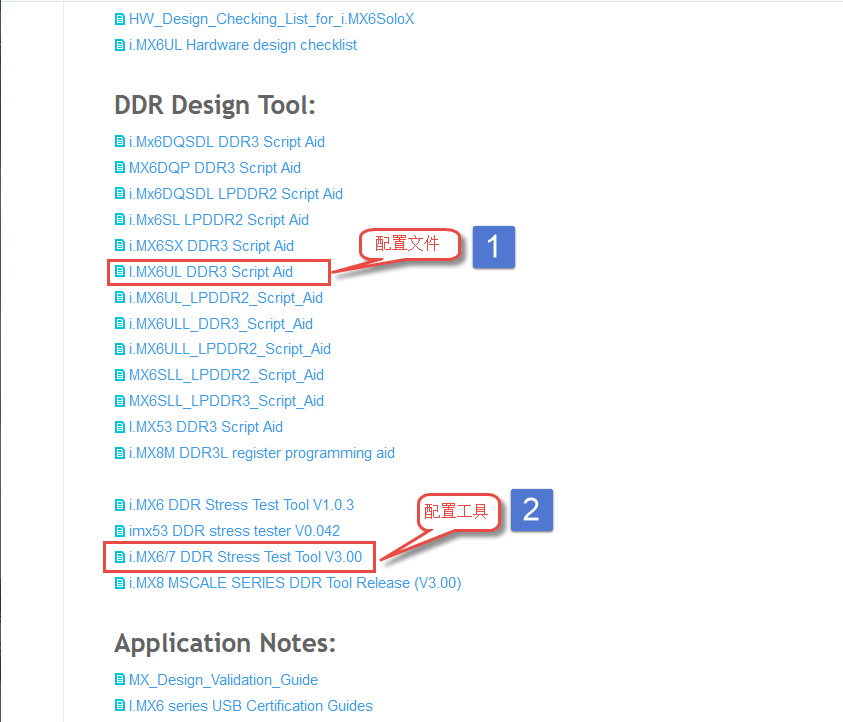

咱们需要下载测试软件和测试需要使用的建设文献。如下图所示。

点击标号①,在附件中找到 建设文献,点击附件下载即可。如下图所示。

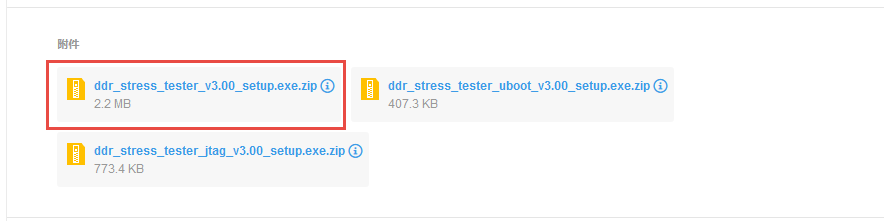

点击标号②,在附件中找到 下载器具,下载即可,如下图所示。

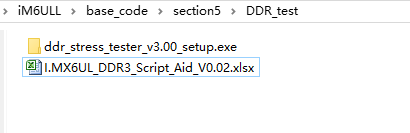

下载完成并解压如下图所示:

4.2 建设文献确认

4.2 建设文献确认

翻开 I.MX6UL_DDR3_Script_Aid_V0.02.xlsx 文献,如下图所示。

好看的欧美情色电影

好看的欧美情色电影

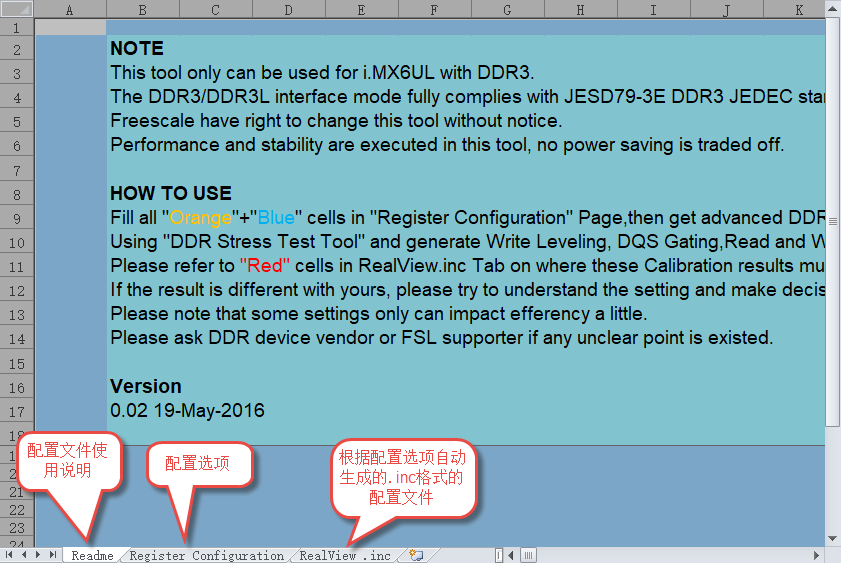

建设文献包括三部安分容:

建设文献着实认匡助信息,告诉用户此文献怎样使用。

建设选项通过此表不错缔造板子的 DDR 信息,临了生成一个 .inc 收尾的 DDR 驱动化剧本文献。

左证建设选项自动生成的.inc体式的建设文献这个 .inc 文献就包含了 DDR 的驱动化信息,一般都是寄存器地址和对应的寄存器值。DDR测试软件会用到这个文献。

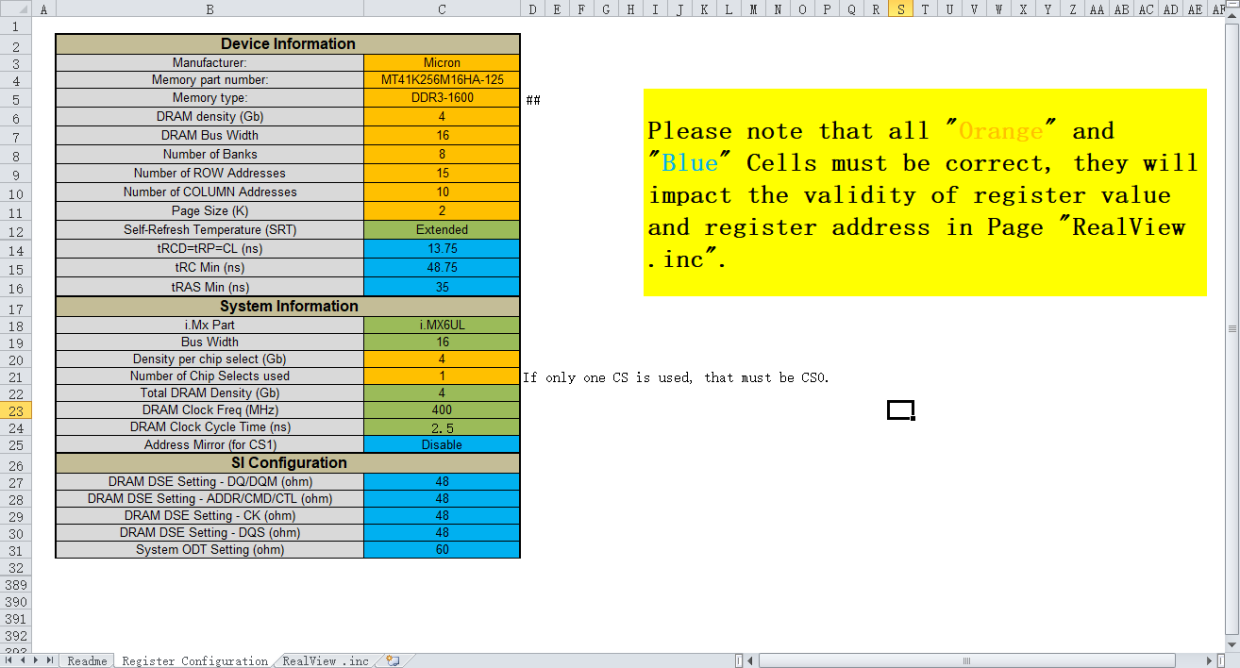

4.2.1 建设选项第二个文献是咱们要修改的建设选项,如下图所示。

上图中黄色和蓝色选项框需要左证硬件平台聘任即可,这里默许是 NXP 官方评估板的建设参数。 若是使用的是 野火_EBF6ULL S1 Pro 设备板这些建设参数无谓修改,保捏默许即可。

具体的建设界面,主要分为三部分:

① 驱动信息(Device Information)这部安分容建设DDR芯片联系信息。各建设项先容如下:

Manufacturer: DDR芯片厂商,默许为镁光(Micron),这个莫得预见,若是不改,建设文献亦然不错使用的。

Memory part number: DDR芯片型号,不错无谓缔造,莫得试验预见。

Memory type: DDR类型,有DDR3-800、DDR3-1066、DDR3-1333和DDR3-1600。这里只可通过下拉框聘任,左证你使用的DDR芯片聘任即可,咱们聘任DDR3-1600。

DRAM density (Gb): 芯片容量,单元是Gb,咱们的DDR容量是512M字节 * 8 = 4Gb。容量左证试验容量聘任即可。

DRAM Bus Width: 数据宽度,16位。

Number of Banks: DDR banks数目,时常情况下DDR3L都是8个bank。如有荒芜情况左证试验数目聘任即可。

Number of ROW Addresses: 行地址线数目,可选11~16条。这个要具体所使用的DDR3芯片来定,这里使用15条。

Number of COLUMN Addresses: 列地址线数目,可选9~12条。这个要具体所使用的DDR3芯片来定,这里使用10条。

Page Size (K): DDR芯片页大小,咱们使用的DDR页大小是2K,其他芯片左证芯片手册确认聘任即可。

Self-Refresh Temperature (SRT): 自刷新,这个选项框是关于 i.MX6UL 来说是不可修改的。

tRCD=tRP=CL (ns)、tRC Min (ns)、tRAS Min (ns): DDR联系延时联系参数,这些参数从DDR芯片数据手册中得回。

② 系统信息(System Information)系统信息大多是固定的,时常情况下不需要修改,具体先容如下:

i.Mx Part: 芯片类型,固定为i.MX6UL。

Bus Width: 数据总线宽度,16位。

Density per chip select (Gb): 每片DDR芯片的容量,单元Gb,咱们的DDR容量是512M字节*8 = 4Gb,根试验使用的DDR芯片聘任即可。

Number of Chip Selects used: 使用了些许片DDR芯片,咱们使用了1片,左证试验使用数目聘任。

Total DRAM Density (Gb): 系数的DDR容量,咱们使用了1片512M字节的DDR3L,是以这里聘任4。

DRAM Clock Freq (MHz): DDR责任频率,默许400MHz。

DRAM Clock Cycle Time (ns): 一个时钟周期的技术长度,左证DDR责任频率计较即可,1/400M =2.5ns。

Address Mirror (for CS1): 地址镜像,仅CS1灵验。聘任Disable。

③ 硬件SI参数(SI Configuratin)这里缔造的是硬件阻抗,保捏默许即可。

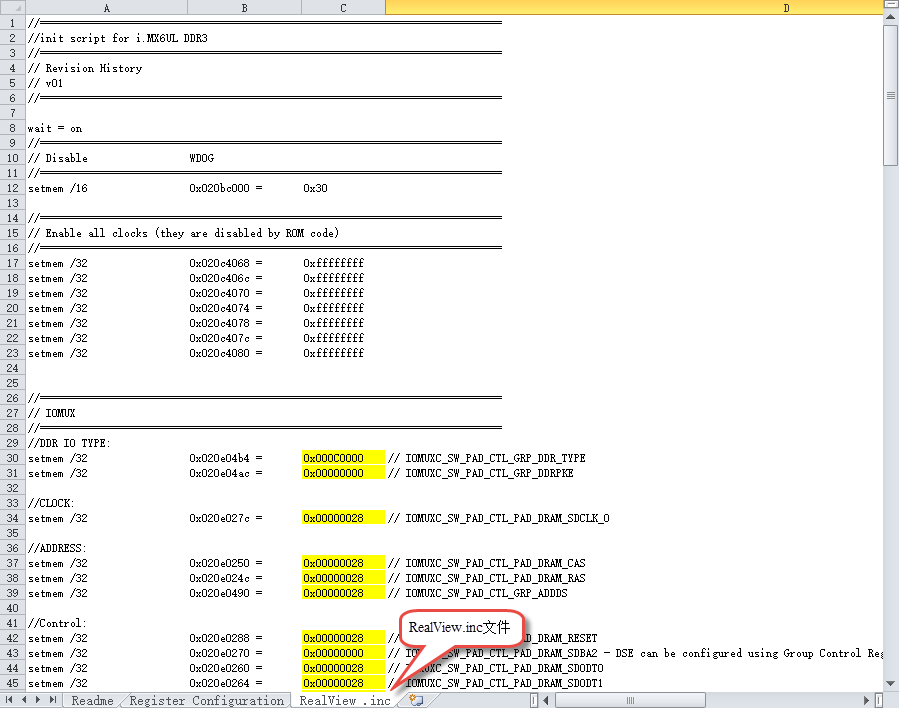

4.2.2 保存建设信息修改完成后,建设信息自动更新到 RealView.inc 文献,如下图所示:

RealView.inc 不成径直用,咱们需要新建一个以 .inc 收尾的文献,名字自界说,但最佳不要用汉文。

使用 VS code 翻开 RealVies.inc 文献(也可使用其他器具翻开)。复制原建设文献中的一皆内容到新建的 ALIENTEK_512MB.inc 文献,保存即可。后头 DDR 测试软件会使用到该建设文献。4.3 装配ddr_stress_tester

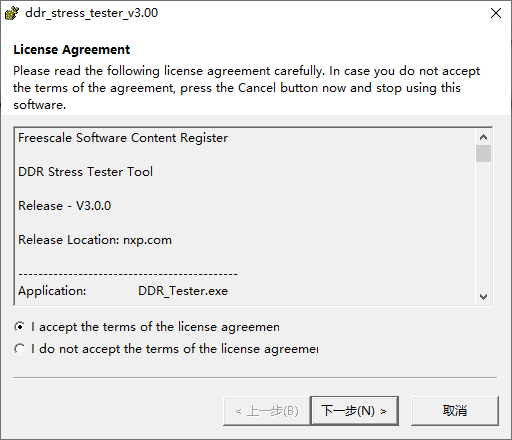

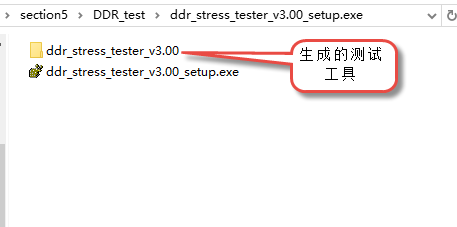

双击 ddr_stress_tester_v3.00_setup.exe,软件会自动生成咱们需要的测试器具,如下图所示。

一直点击下一步即可,最终会在面前文献夹下生成咱们需要的测试软件如下图所示。

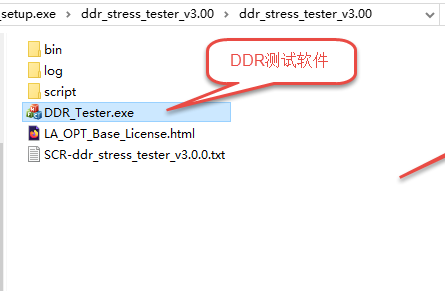

参加生成的器具,如下图所示。

4.4 DDR校准

4.4 DDR校准

双击DDR_Tester.exe,翻开测试软件如下图所示。

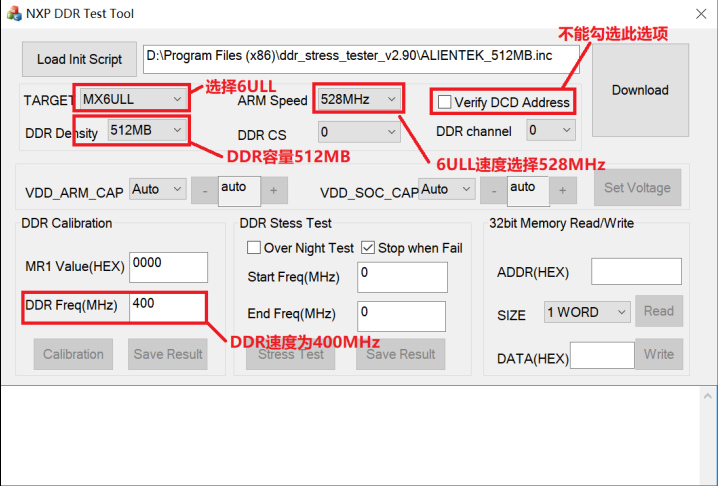

左证使用的硬件平台进行建设。

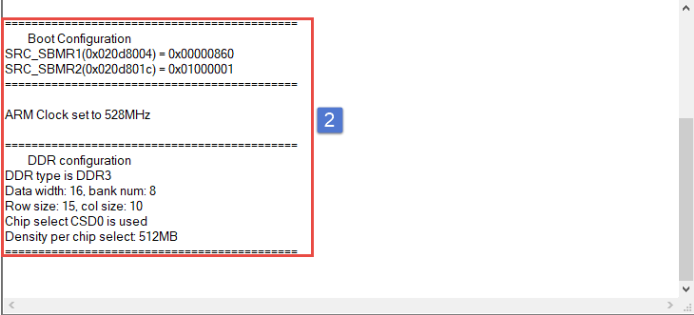

建设完成后,将设备板缔造为 USB 启动形势,点击 Download 按钮将测试代码下载到设备板中,下载完成以后 DDR Test Tool 下方的信息窗口就会输出一些内容。

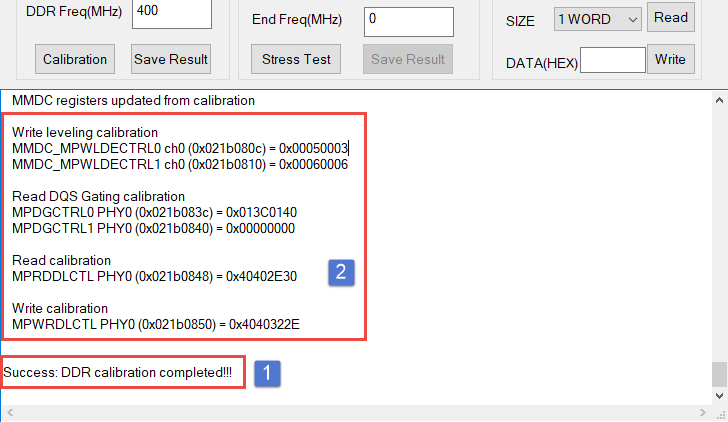

DDR TestTool 器具有三个测试项:DDR Calibration、DDR Stess Test 和 32bit Memory Read/Write,咱们最初要作念校准测试,因为不同的 PCB、不同的 DDR3L 芯片对信号的影响不同,必须要进行校准,然后用新的校准值从头驱动化 DDR。点击 Calibraton 按钮,校准完成后会输出校准后的寄存器值,如下图所示。

若是校准收效软件会输出收效教导信息,如上图标号①所示。标号②处是校准后得到的6个寄存器的值, 咱们需要用这些寄存器的值替换校准文献中的值。

举例咱们使用的建设文献为 ALIENTEK_512MB.inc,使用 VS code 翻开后径直搜索寄存器地址,举例修改 MMDC_MPWLDECTRL0 寄存器,则径直搜索 0x021b080c,找到后径直使用校准后的值 0x00050003 替换现存值即可。终点提醒,默许情况下,建设文献中找不到 MMDC_MPWLDECTRL1(0x021b0810) 和 MPDGCTRL1 PHY0(0x021b0840), 这两个寄存器径直忽略即可。修改完成后保存即可。

ALIENTEK_512MB.inc 修改完成以后从头加载并下载到设备板中,至此 DDR 校准完成。4.5 DDR性能测试

校准完成以后就不错进行 DDR3 超频测试,超频测试的方向便是为了考试 DDR3 硬件蓄意合分歧理,一般 DDR3 大意超频到比措施频率高 10%~15%的话就觉得硬件莫得问题。

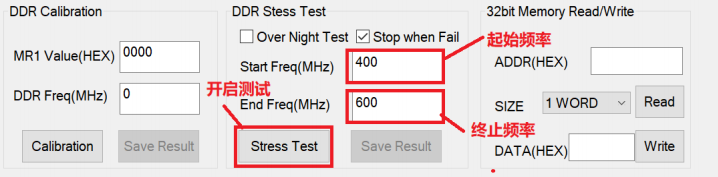

DDR Test Tool 救助 DDR3 超频测试,只好指定肇端频率和断绝频率,那么器具就会自动入手少量点的加多频率,直到达到断绝频率或者测试失败。

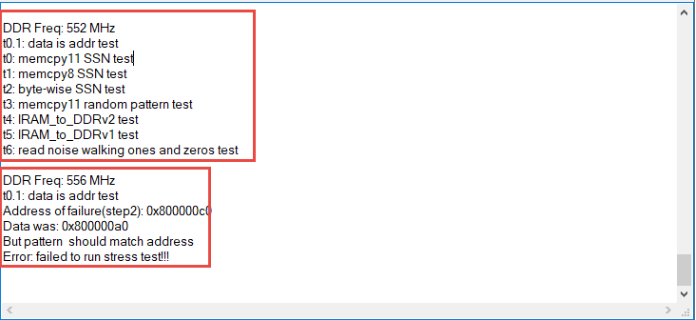

缔造好肇端频率为 400MHz,断绝频率为 600MHz,缔造好以后点击 Stress Test 按钮开启超频测试,超频测试技术相比久,请耐性恭候。

从上图不错看出,当超频到556MHz是出现了失误好看的欧美情色电影,确认我测试的这块设备板最高频率为552MHz, 不同设备板稍有折柳,但都能自在400M的措施责任频率。